Wistron 14088-1 TAHOE_MT H110���幤�����̺���

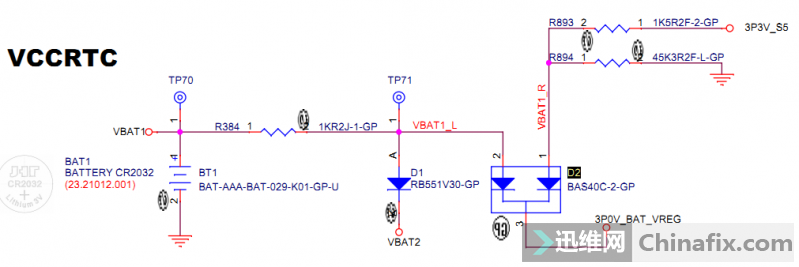

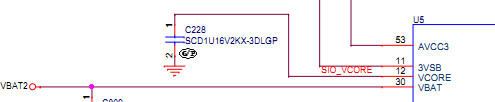

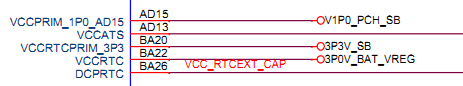

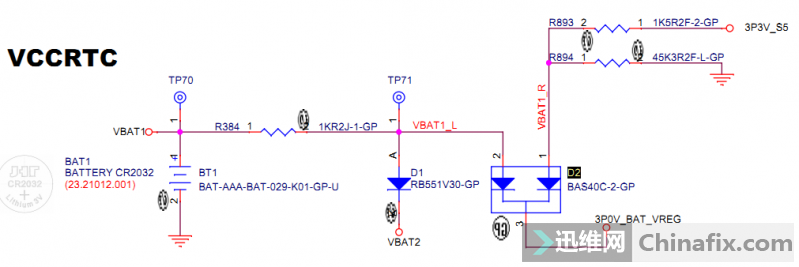

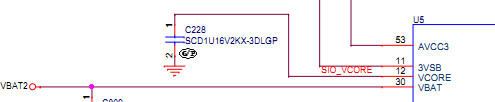

1���]���Դǰ����3V�~��늳�BT1�^���R384�a��VBAT1_L��VBAT1_L�^���O��D1�a��VBAT2���͵�IOоƬU5��IT8617E����30��VBAT���_��

VBAT2�^���O��D2�a��3P0V_BAT_VREG���o���BA22��VCCRTC���_RTC�·��늡�

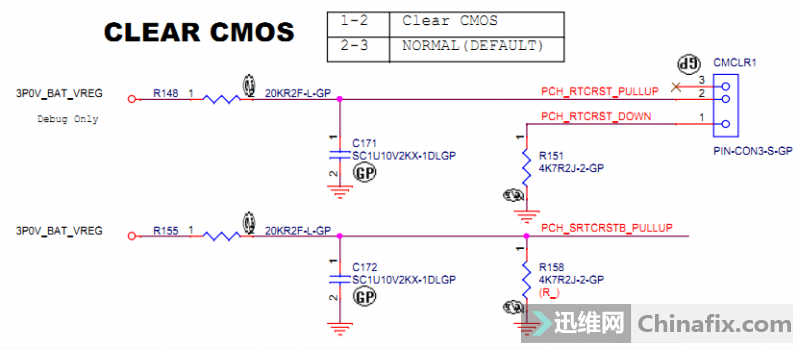

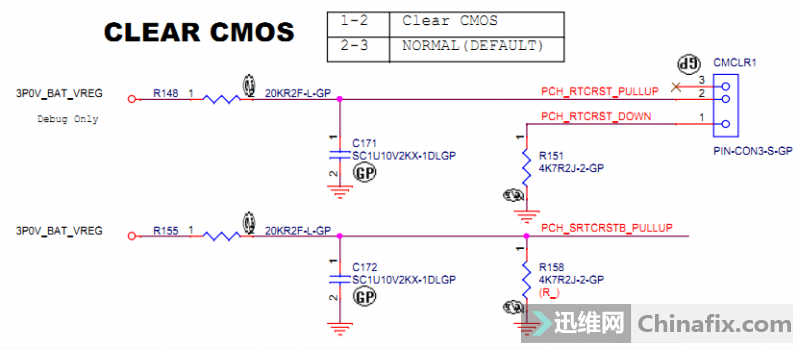

2��3P0V_BAT_VREG���^���R148���B��CMOS��ñ���o���BC10��RTCRST#���ṩ���ƽRTCRST#��

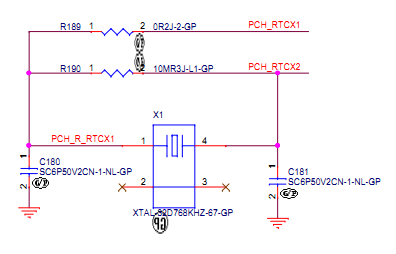

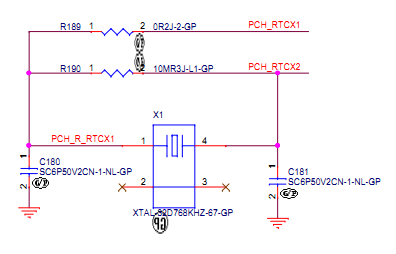

3����o����X1��늣�����X1���a��32.768KHz�o��

4������ATX1��ݔ��V_12P0_A���C��늡�

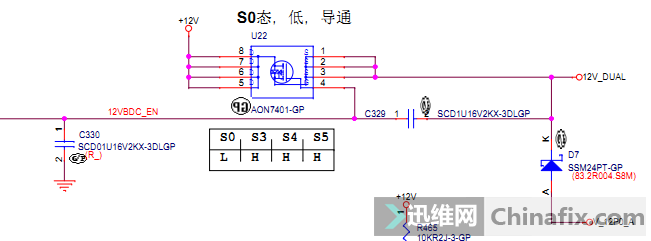

V_12P0_A��D7�a���pͨ����늵�12V_DUAL��

12V_DUAL�^PR130�ȸ���PWR_5V3D3V_VIN��

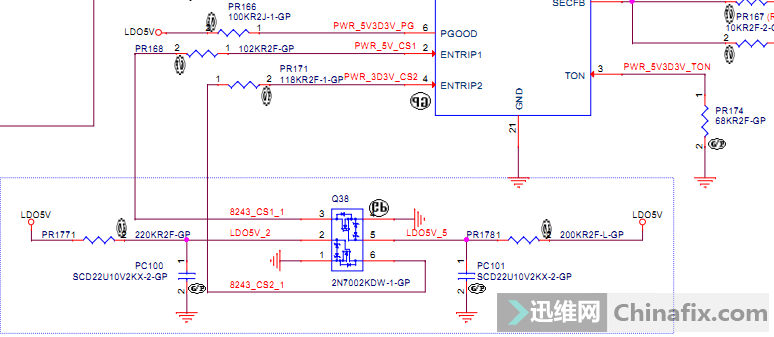

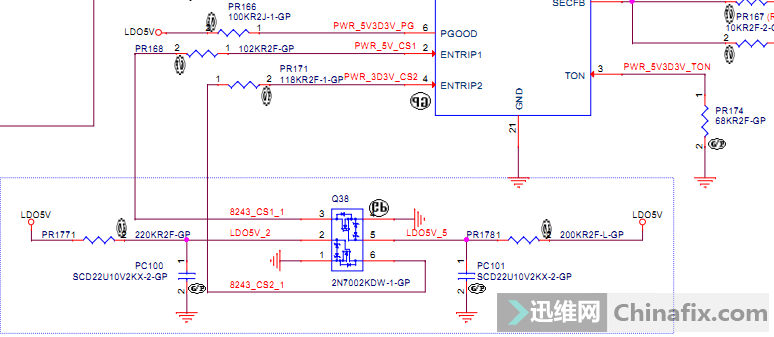

PWR_5V3D3V_VIN�o���CоƬPU35��RT8243B����늣�PU35��RT8243B����14��LDO5��ݔ��LDO5V늉���

LDO5V����Q38��ͨ���a��PWR_5V_CS1��PWR_3D3V_CS2�͵�PU35��RT8243B����2��ENTRIP1����4��ENTRIP2���_���_��PU35��RT8243B��������PU35��RT8243B������MOSݔ��PWR_5V��PWR_3D3V��

PWR_5V�^PR5418�ȸ���5V_S5��PWR_3D3V�^PR138�ȸ���3P3V_S5��

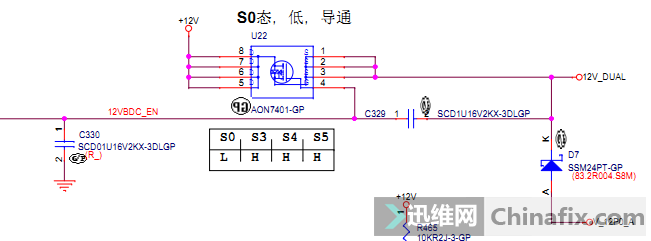

5V_S5��3P3V_S5�鱾�C�Ĵ��C늉������|�l���늉���+12Vͨ�^U22��12V_DUAL���pͨ����늮a������

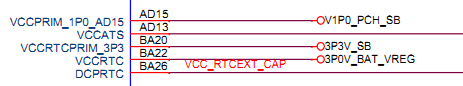

5��3P3V_S5�������˯�ߴ��C늉��o��VCCDSW_3P3�����_W15��BA24�_��3P3V_S5߀�͵�IOоƬU5��IT8617E����11��3VSB���_��

��IOоƬU5��IT8617E���z�y��늉������ĵ�7��DPWROK/GP23���_�l�����˯�ߴ��C늉���PCH_SIO_DPWROK��̖�o�����AV11��DSW_PWROK���_��

�ژ��BB13��SLP_SUS#���_�l��SLP_SUSB���͵�IOоƬU5��IT8617E����64�_��

��SLP_SUSB�͵�U57��TPS22966DP����6��ON2���_������U57�a�������C늉�3P3V_SB,�͵����VCCPRIM_3P3���_BD3��BE3��BE4���������_��

�������C늉�3P3V_SB���oIOоƬU5��IT8617E����28��SYS_3VSB���_��

��3P3V_SB�^0ohm���R482�����3P3V_PCIVAUX���oPCI��PCI_E�ۡ�

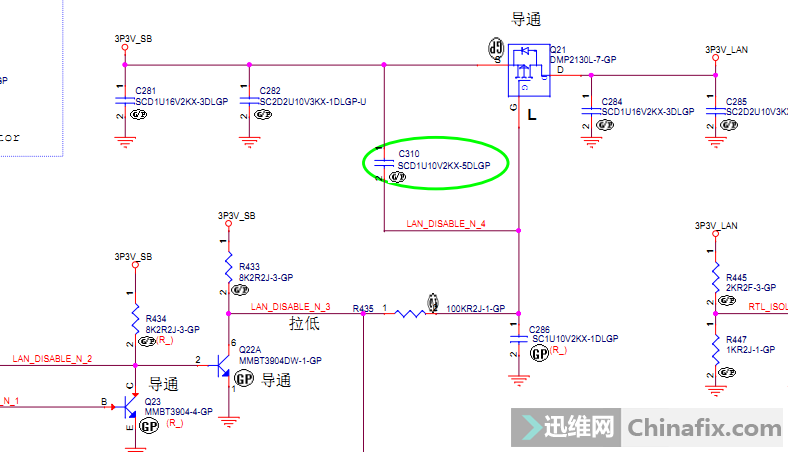

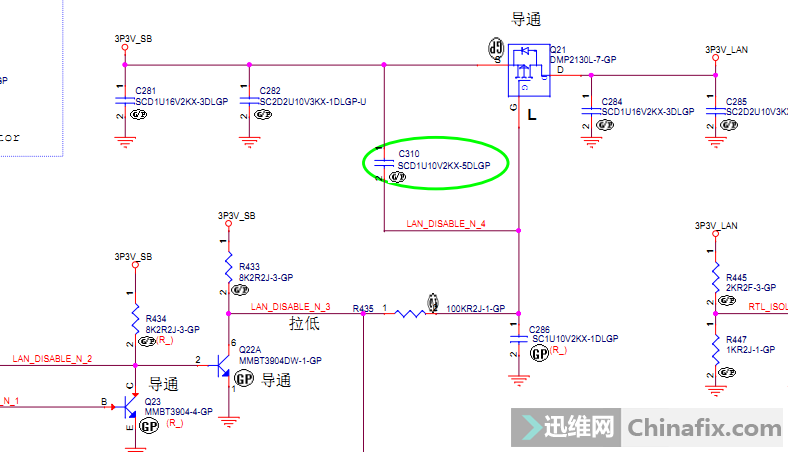

��3P3V_SB���^�·�D�Q����Q21��ͨ���a��3P3V_LAN�����o�W��оƬU10��RTL8111G���ĵ�32��AVDD33���_��

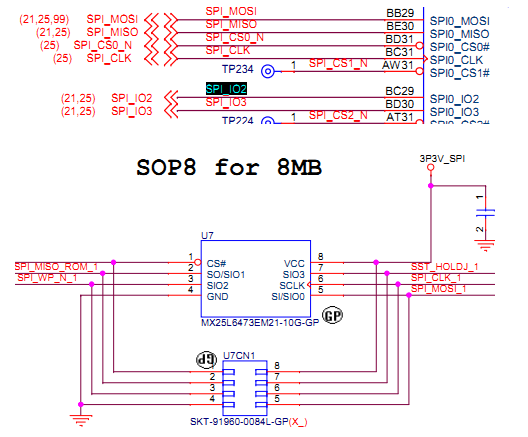

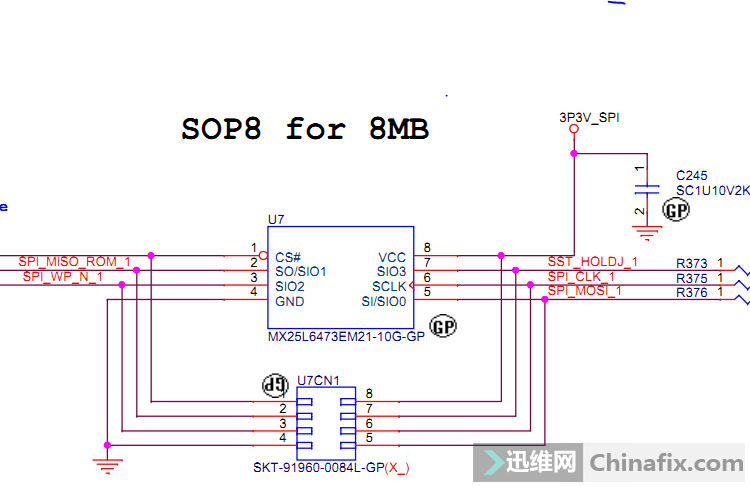

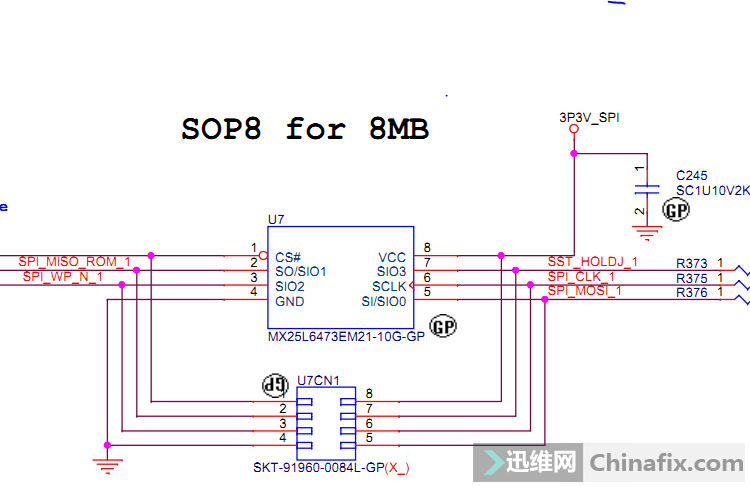

��3P3V_SB�^0ohm���R368�����3P3V_SPI�����o���VCCSPI���_BE41��BE42��BE43��

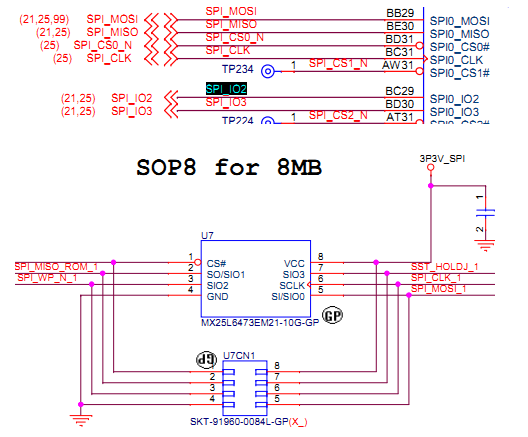

��3P3V_SPI�oBIOSоƬU7��늡�

��3V���C늉�3P3V_SB�������ٽ����a��1V���C늉�VCCPRIM_1P0��

PU14��RT8237C�����Ʈa��PWR_1D0V늉����^PR213�Ⱥ����V1P0_PCH_SB,�ͽo���VCCPRIM_1P0���_��늡�ͨ�^�D�Q��o����������_��늡�

6��IOоƬU5�z�y���C늉�������42��RSMRST#���_�l�����C늉��ã�RSMRST#��RSMRST_SIO_N��̖���o���BA11��RSMRST#���_��

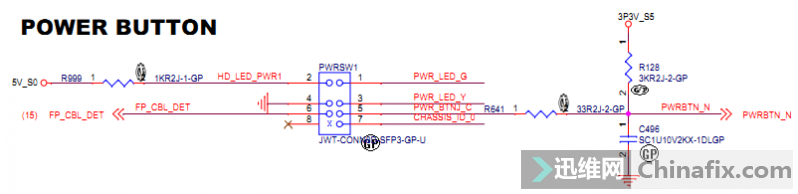

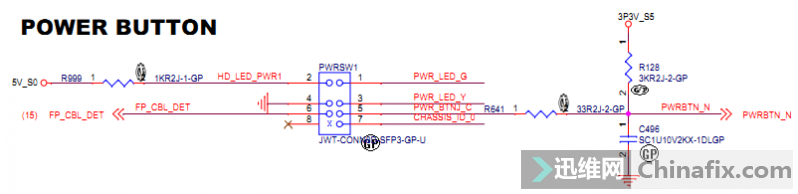

7���Ñ��������PWRSW1�ϵ��_�P���a��3.3V_0V_3.3V��׃����̖PWRBTN_N���͵���IOоƬ��IT8617E����34��PANSWH#���_��

8��IO��32��PWRON#���l��3.3V_0V_3.3V��׃��Ո���_�C��̖PWRBTN_N_SIO���͵���PCH��AT13��PWRBTN#���_��

9����l�����S�_�C��̖SLP_S*#:

��PCH��BB13��SLP_SUS#���_�l��SLP_SUSB��̖��

�ڏ�AW15��SLP_S3#���_�l��SLP_S3_N��̖��

�ۏ�BD15��SLP_4S#���_�l��SLP_S4_N��̖��

����SLP_SUSB�͵�IO��64��VLDT_EN/SLP_SUS#/GP63���_��SLP_S3#�ͽoIO��34��PANSWH#���_����ʾ���S�_�C��

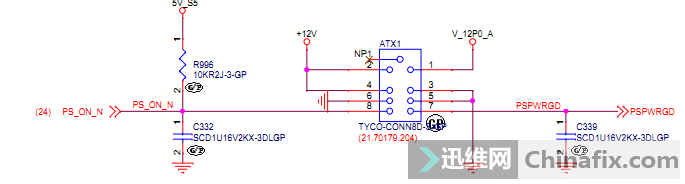

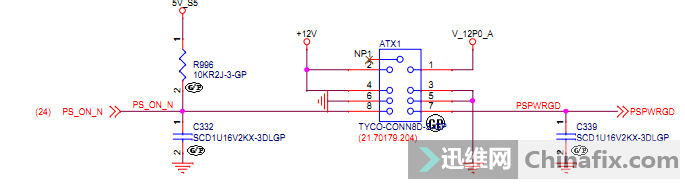

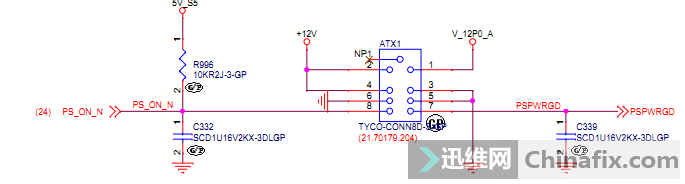

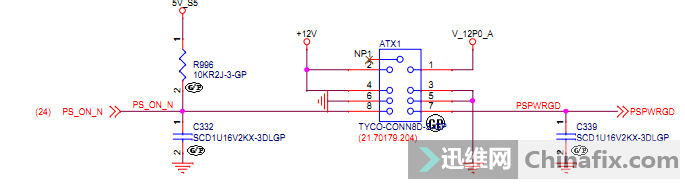

10��IOоƬ��35��PSON#���_�l�����m���ƽPS_ON_N��̖���͵�ATX1���^��8��PSON#���_�����;G���_�C��

11��ATX1��2��4�_ݔ����+12V��

12����SLP_SUSB�͵�U57��TPS22966DP�����Ʈa��5V_S0��3P3V_SB��

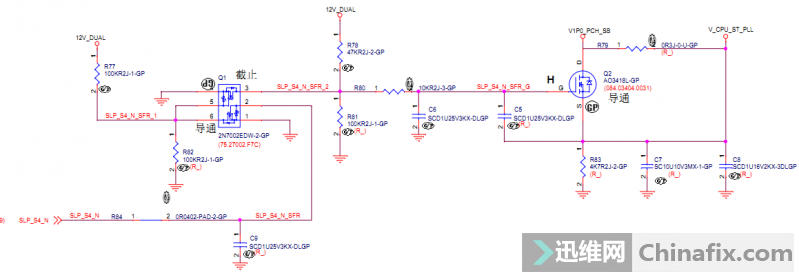

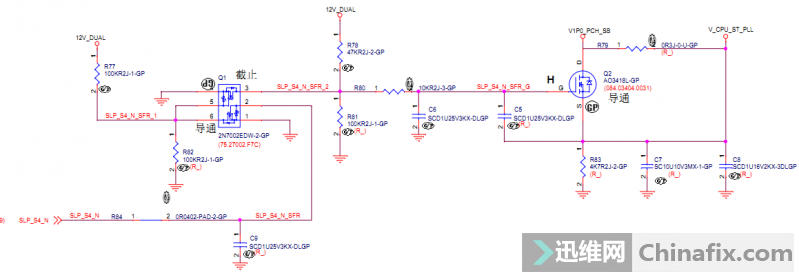

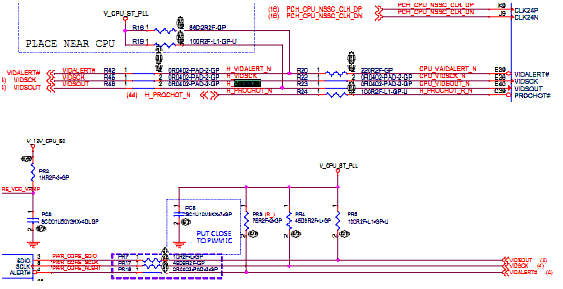

��SLP_S4#����Q1��Q2��V1P0_PCH_SB�D�QV_CPU_ST_PLL���oPCH��1.05V�� VCCST/VCCPLL���_��늡�

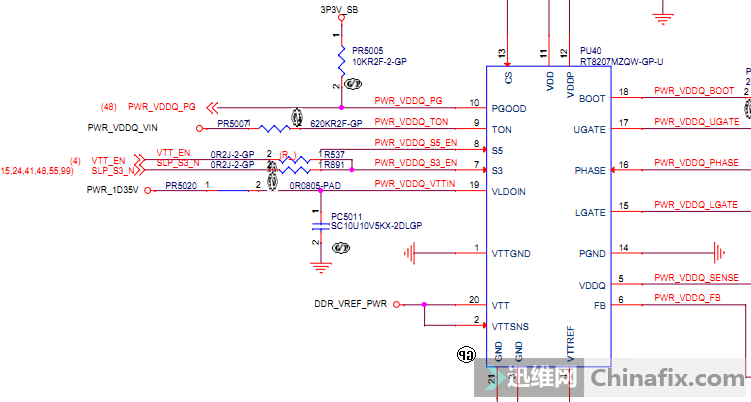

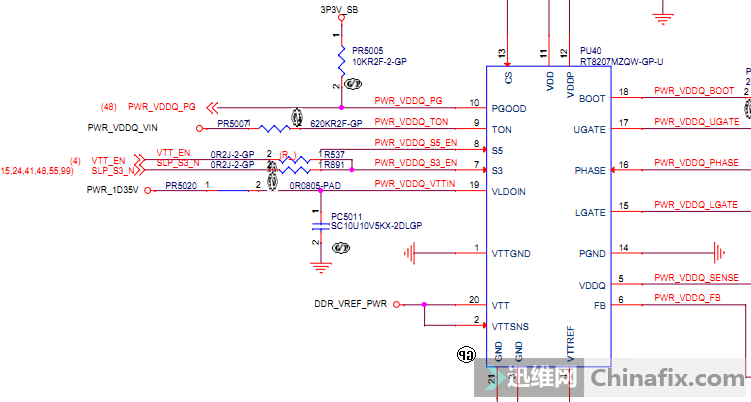

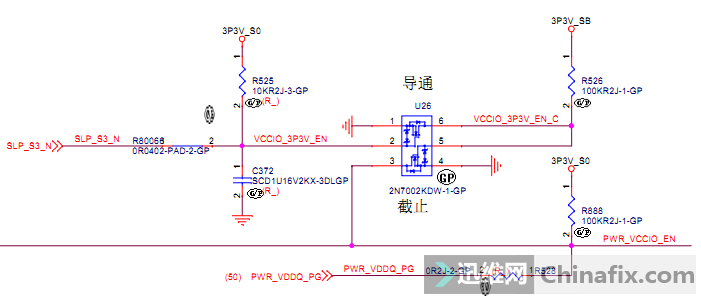

��SLP_S4�^0ohm���R885����PWR_VDDQ_S5_EN���͵�PU40��RT8207M����8��S5���_��SLP_S3_N�͵�7��S3���_����ͬ�_��PU40��������PU39��PU41ݔ��PWR_1D35V�ȴ�����늡�

PWR_1D35V�ȴ�����늮a�����^PR191�ȹ��c����V_SM����CPU��VDDQ���_�̓ȴ��VDD���_��늡�

V_SM_VTT�Įa����CPU��늹���оƬ��20��VTT���_ݔ��0D675V��DDR_VREF_PWR,�^PR201���c����V_SM_VTT. ��ȴ��VTT���_��늡�

��PU40��RT8207M���ĵ�10��PGOOD���_ݔ��PWR_VDDQ_PG��̖���ĵ�20��VTT���_ݔ��DDR_VREF_PWR��̖��

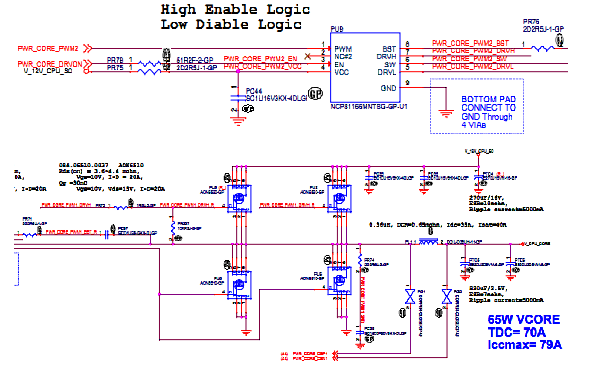

13���a��1.05V��VCCIO���

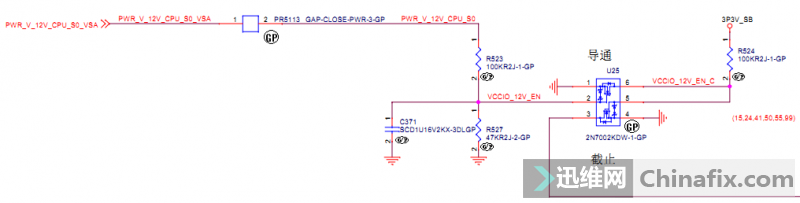

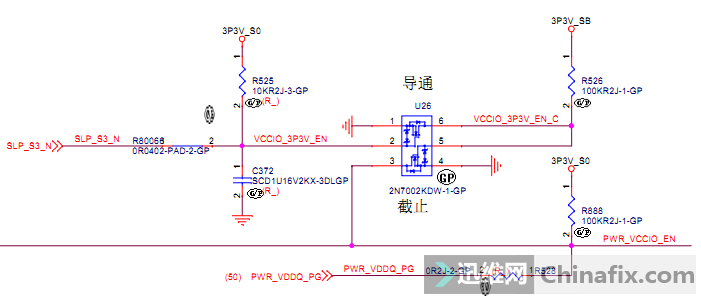

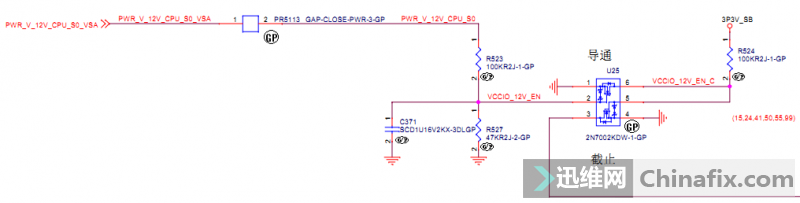

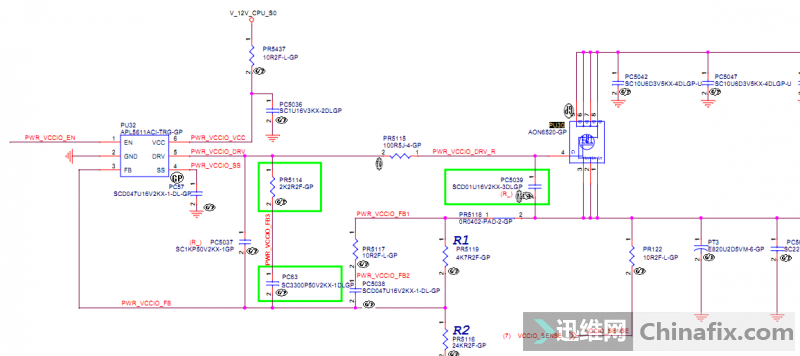

PWR_V_12V_CPU_S0_VSA����U25��SLP_S3_N����U26�a��PWR_VCCIO_EN��ȥ�_��PU32��APL5611A��������

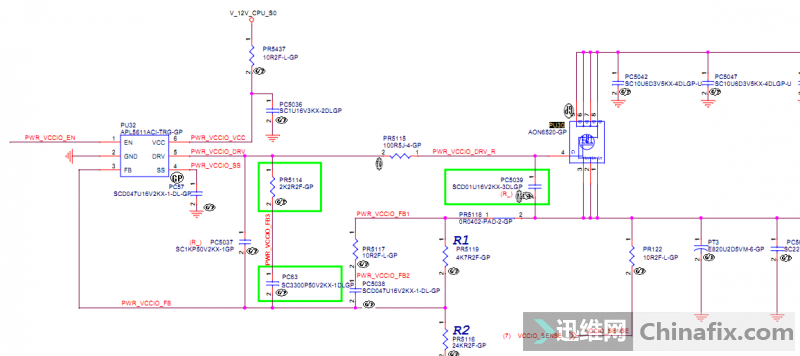

PU32����PU30ݔ��CPU��1.05V��VCCIO���V_CPU_IO�����oCPU��VCCIO���_��

14��1.05V����Ĺ���������Ʈa��VCCSA늉�V_CPU_SA�����a��CPU��늵��_����̖,��һ�㲻���a��CPU��늣�VBOOT=0V��

��SLP_S3_N����U30�a��VR_ENABLE��̖��

��VR_ENABLE����PQ1ȥ�_��PU28��RT8237������PU27ݔ��V_CPU_SA��

��V_CPU_SA�oCPU��VCCSA���_��늡�

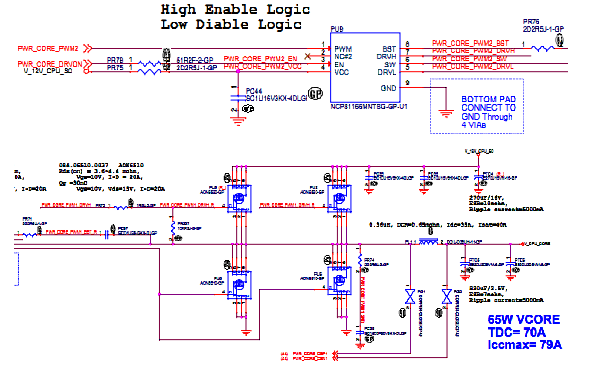

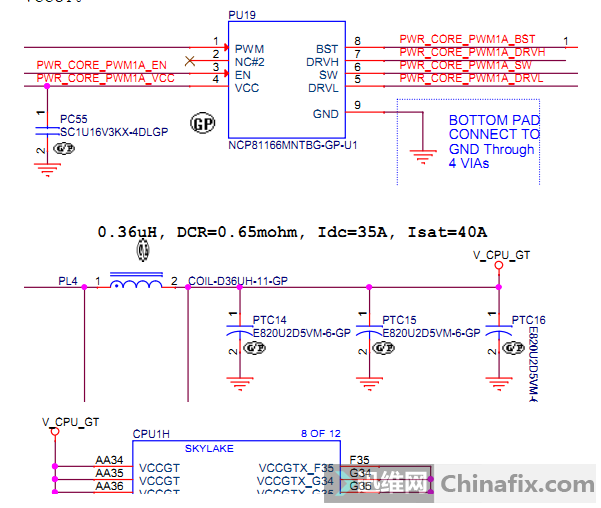

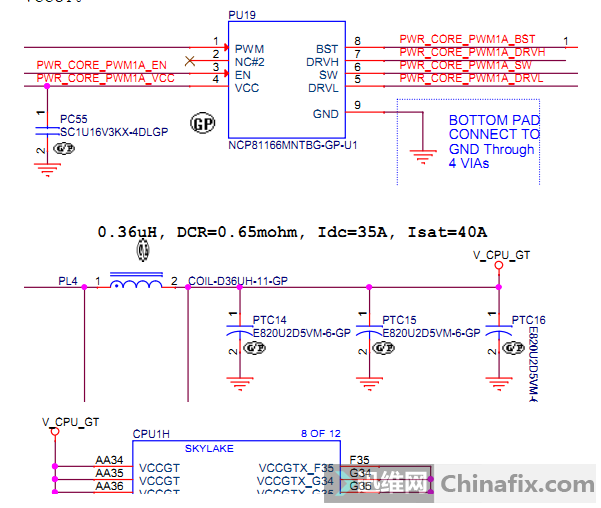

��VR_ENABLE�͵�CPU�Դ����оƬPU1��NCP81203����2��EN���_��ȥ�_��PU1���������˕r�����a��CPU��늣�VBOOT=0V��

15��CPU�Դ����оƬPU1��NCP81203����6��VRDY���_�l��VR_READY��̖����U3�D�Q�l�����ƽ��PCH_PWROK��̖���͵�PCH��AW11��PCH_PWROK���_����ʾоƬ�ѽ��ʂ�ã��a��CPU��늡�

16��ATX1�Դ�ĵ�7�_�ӕr�l���Ҿ���PSPWRGD���ͽoIOоƬ��IT8617E����6��ATXPG/GP53���_��

17��IO�z�y��·늉���PSPWRGD������37��PWRGD3/CPU_PG/SDA0���_�l��PWROK3��̖���^0ohm������PCH_SYSPWROK���ͽo���AY1��SYS_PWROK���_��

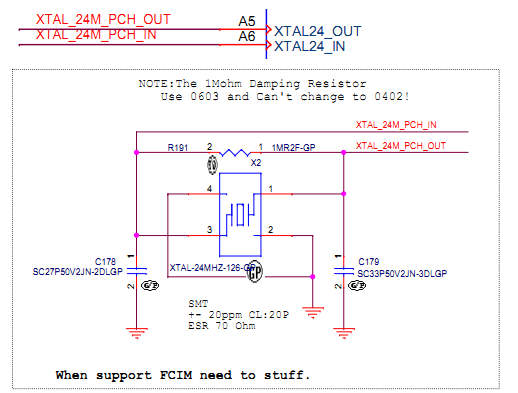

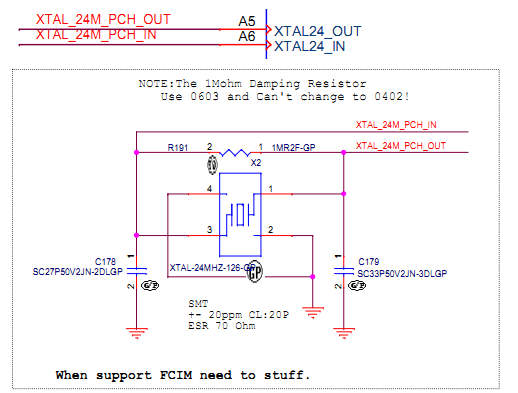

18�����24M����X2�����xȡBIOSоƬU7�Ĕ�����

19���٘�l���r���̖���ͽo������O�䡣

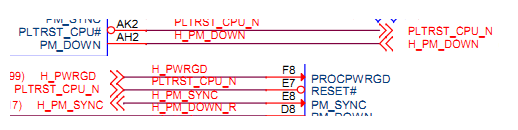

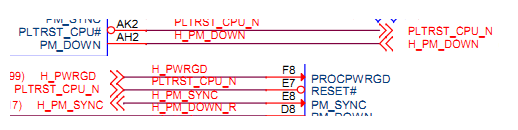

�ژ��AM3��PROCPWRGD���_�l��H_PWRGD��̖���ͽoCPU��F8��PROCPWRGD���_��

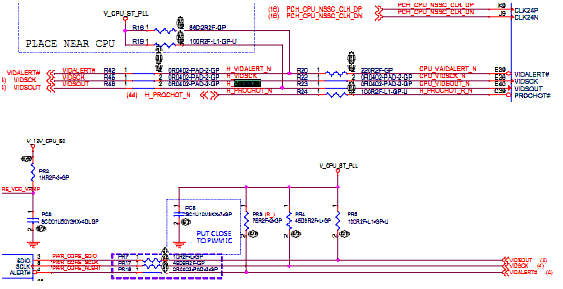

��CPU�l��SVID��̖VIDSOUT��VIDSCK ��VIDALERT#�oCPU���оƬPU1��3��SDIO����5��SCLK����4��ALERT#���_��

��CPU���оƬPU1��NCP81203������ݔ��CPU��늡�

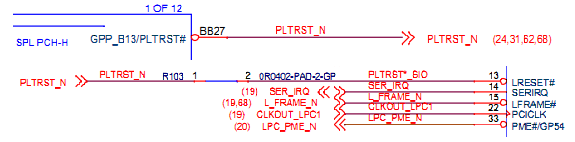

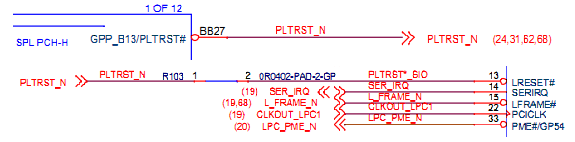

20���٘�l��ƽ�_��λ��PLTRST#��PLTRST_N�oIOоƬ��13��LRESET#���_����λIO��

��PLTRST_N�͵��W��оƬU10��19��PERST#���_��λ�W����

PLTRST_N��λNGFF1оƬ��߀�͵�LPC1��3�_��

��IOоƬ��IT8617E����10�_ݔ��PLTRST_PCIE_SLOTS_N��̖���͵�PCIE�۵�A11�_����λPCI_E�ۡ�

PLTRST_PCIE_SLOTS_N��̖߀�͵�U54��XIO2001����H11��PERST#���_����λU54��XIO2001����

21�����AK22�_�l��CPU�ď�λ��PLTRST_CPU#��PLTRST_CPU_N��̖���͵�CPU��E7��RESET#���_����λCPU��

22��CPU�_ʼ������ͨ�^���xȡBIOS���_ʼ�ԙz�ܴa��

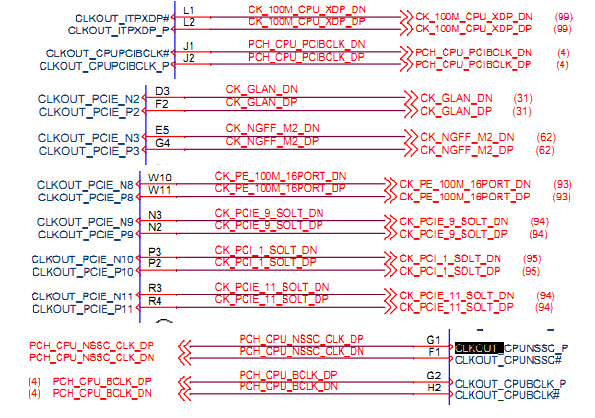

23��H110�ԙz�^�ȴ��CPU�l���ڶ���SVID�����Ʈa�����@���VCCGT��

|